2013년10월12일 46번

[마이크로전자계산기] fetch cycle 수행시 적합하지 않은 마이크로 오퍼레이션은?

- ① IR ← DBUS, RD ← 0

- ② ABUS ← PC, RD ← 1

- ③ M[ABUS] ← DBUS, WR ← 1

- ④ DBUS ← M[ABUS]

(정답률: 59%)

문제 해설

적합하지 않은 마이크로 오퍼레이션은 "IR ← DBUS, RD ← 0"이다. 이는 fetch cycle에서는 필요하지 않은 오퍼레이션이기 때문이다. fetch cycle에서는 PC(Program Counter)의 값을 ABUS(Address BUS)로 전송하고, 해당 주소의 명령어를 M(Memory)에서 읽어와 DBUS(Data BUS)로 전송한 후 IR(Instruction Register)에 저장한다. 따라서 IR ← DBUS, RD ← 0은 fetch cycle에서는 필요하지 않은 오퍼레이션이다.

"M[ABUS] ← DBUS, WR ← 1"은 ABUS에 저장된 주소에 DBUS에 저장된 값을 쓰는 오퍼레이션이다. 이는 fetch cycle에서는 해당 명령어를 읽어오는 오퍼레이션으로 필수적이다.

"M[ABUS] ← DBUS, WR ← 1"은 ABUS에 저장된 주소에 DBUS에 저장된 값을 쓰는 오퍼레이션이다. 이는 fetch cycle에서는 해당 명령어를 읽어오는 오퍼레이션으로 필수적이다.

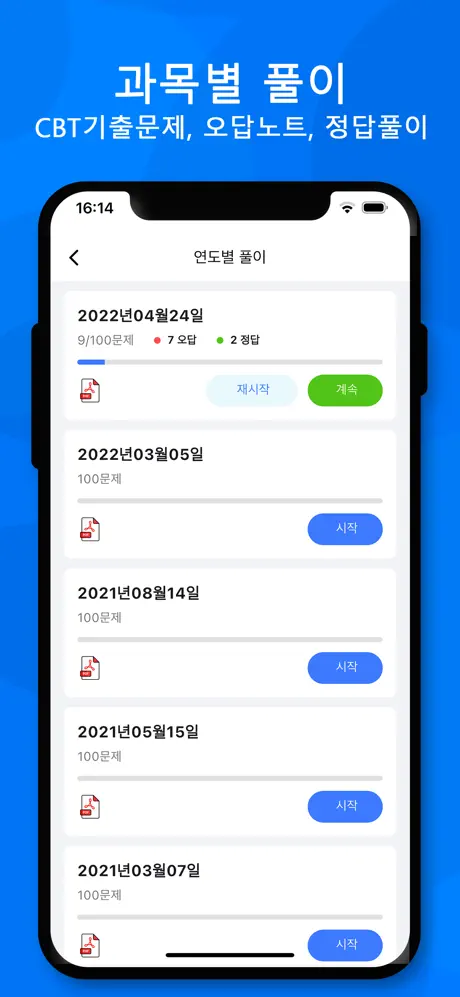

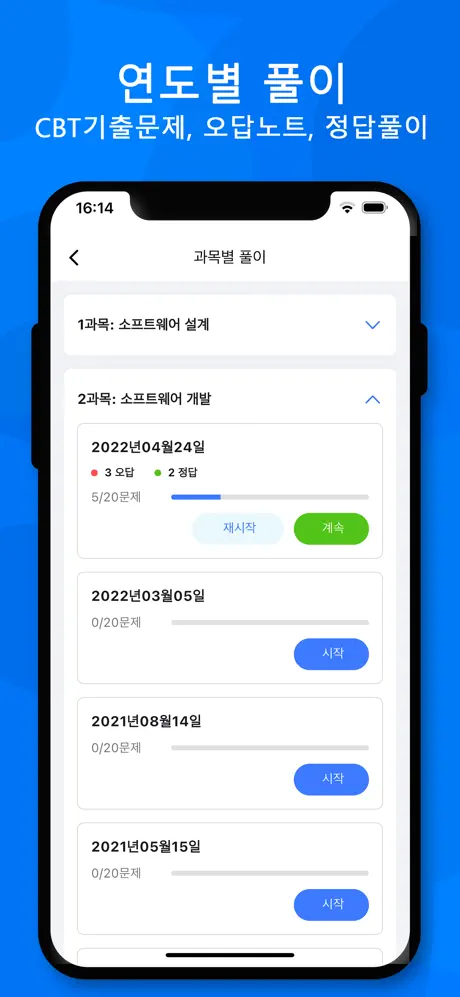

연도별

진행 상황

0 오답

0 정답